平成 28 年 12 月 5 日

報道機関 各位

東北大学原子分子材料科学高等研究機構(WPI-AIMR) 東北大学流体科学研究所(IFS)

# 高性能・サブ 10nm・3次元フィン型ゲルマニウム トランジスタを世界で初めて実現

超低損傷・低温中性粒子ビーム加工プロセス技術を用いてー

### 【概要】

東北大学原子分子材料科学高等研究機構(WPI-AIMR)および流体科学研究所(IFS)の寒川誠二教授のグループは、アジア半導体デバイス開発拠点の中核である台湾の国立交通大學(NCTU)、国立ナノデバイス研究所(NDL)と共同で、独自技術である超低損傷・中性粒子ビーム技術(加工、酸化プロセス)を用いた「高性能サブ10nm・3次元フィン型ゲルマニウムトランジスタ」を世界で初めて作製することに成功しました。

半導体産業においては世界的な競争のもと、新材料の導入や微細化研究が盛んです。 特に MOS トランジスタは半導体産業の最大の牽引車であり、Internet of Thing (IoT) や人工知能(artificial intelligence: AI)において国際競争を勝ち抜くために、その高 性能化の研究は極めて重要です。集積回路の高性能化には回路の微細化が不可欠ですが、 今まで、微細化した回路素子からのリーク電流(\*1)による発熱が大きくなりすぎて「技術 世代22ナノメートル」以降の超高集積回路の実現は難しいとされてきました。この壁を 打ち破るため、今回本研究グループは、シリコンに比べて損傷が入りやすく加工形状の 制御が難しいゲルマニウムの塩素中性粒子ビーム(\*2)による「高精度無損傷異方性加工に よるフィン型チャネル構造の作製」、酸素中性粒子ビームによる「室温異方性酸化による フィン型チャネル形状制御」と「高品質ゲルマニウム酸化膜の形成」を同時に実現するこ とで、サブ 10nm・3 次元フィン型ゲルマニウムトランジスタ構造試作を行い、電気特性 を測定しました。その結果、世界で初めて「サブスレッショルド・スイング(SS)<sup>(\*3)</sup>を N型トランジスタで 70mV/dec、P型トランジスタで 87mV/dec、オンオフ電流比を 105以 上」を同時に実現することに成功しました。これにより、リーク電流による発熱に起因す る技術的限界は乗り越えられ、今後、サブ 10nm・3次元フィン型ゲルマニウム MOS トラ ンジスタの開発が大きく前進することが期待されます。

本研究成果は、2016 年 12 月 5 日からサンフランシスコで開催される IEEE International Electron Device Meeting (IEDM 2016)で発表されます。

# 【本件に関する問い合わせ先】

(研究内容について)

東北大学原子分子材料科学高等研究機構(WPI-AIMR)·流体科学研究所(IFS) 教授 寒川誠二 TEL: 022-217-5240 (報道担当)

東北大学原子分子材料科学高等研究機構(WPI-AIMR) 広報・アウトリーチオフィス 清水修 TEL: 022-217-6146

#### 【研究の背景】

半導体産業においては世界的な競争のもと、新材料の導入や微細化研究が盛んに行われています。現在、特に MOS トランジスタが半導体産業の最大の牽引車となっており、IoT や AI における国際競争を勝ち抜くために、その高性能化の研究は極めて重要です。集積回路の高性能化には回路の微細化が不可欠ですが、現在の 2 次元平面的な広がりを必要とする素子技術では、微細化した回路素子からのリーク電流による発熱が大きくなりすぎて、「技術世代 22 ナノメートル」以降の超高集積回路の実現は難しいとされてきました。

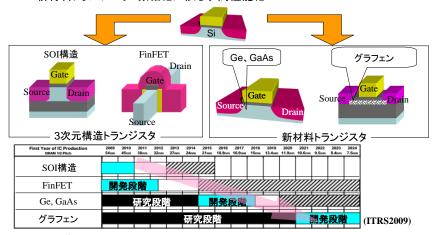

この壁を打ち破るため、チャネル材料<sup>(\*4)</sup>にゲルマニウムを用いた 3 次元フィン型 MOS トランジスタの開発が精力的に進められています(図 1)。そのゲルマニウム MOS トランジスタにおける製造上および特性上の最大の課題は「エッチングプロセスにおける加工面の損傷の抑制とチャネル形状の制御」およびゲート酸化膜形成時における「ゲルマニウムおよびゲルマニウム酸化膜の界面準位<sup>(\*5)</sup>をいかに下げるか」という点にあります。プラズマエッチングを用いたゲルマニウムの加工ではプラズマから紫外線が照射され高密度の欠陥が形成されるとともに、欠陥生成面のエッチングが促進されるのでサイドエッチングが生じるために寸法制御が難しいことが知られています。また、3 次元フィン型ゲルマニウムチャネル側壁の酸化プロセスではゲルマニウム酸化物(GeOx: Ge サブオキサイド)は熱的に不安定であるため熱酸化プロセスを用いると高密度な界面準位が形成されることも知られています。そのため、高性能 3 次元フィン型 Ge MOSFET の実現のためには、「無損傷異方性加工によるチャネル側壁欠陥生成の抑制と寸法・形状制御」および「低温無損傷側壁酸化」が重要となります。

# 【研究の内容】

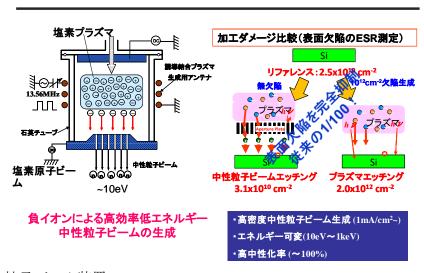

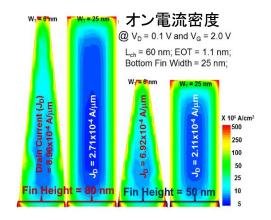

今回、本研究グループは、ゲルマニウム加工に塩素中性粒子ビームを用いました。この手法を使えば、プラズマからの紫外線照射の完全抑制によりフィン型チャネル側壁への欠陥を 1/100 以下に抑えられるため (図2)、マスク通りの垂直加工が可能となり、寸法制御をすることができます。また、形成された 3 次元フィン型チャネル構造を酸素中性粒子ビームによる室温での異方性酸化を行い、フッ酸で除去することで、サブ 10nm ゲルマニウムフィンチャネル構造の上部を細らせて三角形状が実現できるピーキングプロセスを開発しました。その後、再度、室温無損傷中性粒子ビーム酸化によりゲート絶縁膜を形成して 3 次元フィン型ゲルマニウム MOSFET 試作を行いました (図3)。

その結果、N型、P型それぞれでサブスレッショルド・スイング (SS)が 70mV/dec、87mV/decで動作オンオフ電流比が  $10^5$ 以上を同時に実現することに世界で初めて成功しました (表 1)。

この成果は、3次元フィン型チャネル構造側壁加工の欠陥生成を極力抑制することで高品質な界面を実現できたことと、電界が集中しない理想的なチャネルピーキング形状が実現できたことによるものです(図4)。従来、プラズマ加工プロセスや熱酸化プロセスは、「ゲルマニウムを用いた高移動度 MOS トランジスタの実現」の大きな障害になっておりました。しかし、本研究により、中性粒子ビーム加工や中性粒子ビーム酸化を用いて高品質な界面や形状制御が実現できたことから、今後ゲルマニウム MOS トランジスタの開発が大きく前進することが期待されます。

現在の半導体業界を取り巻く状況として、「如何にしてプロセスダメージ<sup>(\*6)</sup>を克服するか、如何にして低温プロセスを実現するか」という非常に大きな問題があります。これは、半導体 LSI の集積化が進み LSI の構成素子であるトランジスタの更なる微細化に伴い表面に生成する欠陥の電気特性に対する影響が飛躍的に大きくなったことによります。プラズマを用いたプロセスでは励起されたラジカルやイオンにより表面反応は低温で進行するため、従来の熱プロセスに比べて圧倒的に低温のプロセスが実現できます。しかし、プラズマから照射される放射光 (特に紫外線)により、基板表面から数十 nm 以上の深さで欠陥が生成されます。特に形成構造がナノオーダーになりますと、構造全体に欠陥が生成されるためにデバイスとしての機能を果たすことができなくなります。我々は、実用的なプロセス技術の確立を目指して、2001 年より「中性粒子ビームの

各種先端デバイスへの応用に関する検討及び技術開発の研究」に着手してまいりました。今回は Ge MOS デバイスへの中性粒子ビーム酸化の適用と実際の電気特性の向上を実現し、次世代 Ge MOS トランジスタへの超低損傷・低温プロセスの有効性を明らかに示すことに成功いたしました。

# 【今後の展開】

中性粒子ビームによる加工・表面改質・材料堆積技術は、現在の半導体業界が直面している革新的ナノデバイスの開発を妨げるプロセス損傷を解決する全く新しいプロセス技術であると考えられます。また、本技術を用いた装置はプラズマプロセス(\*\*7)として実績がありもっとも安定した装置において用いられているプラズマ源をそのまま用い、中性化のためのグラファイトグリットを付加するだけで実現できるため、今後、数十 nm 以下のナノデバイスにおける革新的なプロセスとして実用化されていくことがおおいに期待されるものです。中性粒子ビーム技術は既に均一大面積プロセスを実現できるプラズマ源を基盤に装置が実現できるため、極めて実用的であり、今後、最先端ナノデバイス製造プロセスにおいて中性粒子ビーム加工技術のみならず、中性粒子ビームを用いた表面改質・修飾技術の研究開発を進めて実用的なデバイス開発を大いに推進していく予定です。今回、超低損傷・低温中性粒子ビーム加工および酸化プロセス技術による高品質3次元フィン型ゲルマニウムMOSFET構造の実現に成功し、実際の電気特性を確認することに成功したことで、実用化に向けて大きく前進しました。すでに、大手装置メーカーと装置化への検討も進んでおり、近い将来の実用化に向けてさらに研究を進めていきます。

#### 【参考図】

#### 次世代トランジスタ

- ・3次元構造トランジスタ: 短チャネル効果の抑制

- ・新材料トランジスタ:微細化に依らず高性能化

図1 先端デバイス開発ロードマップ

図2 中性粒子ビーム装置

図3 塩素中性粒子ビームによるフィン型ゲルマニウムチャネル構造エッチングと酸素中性粒子ビームによる側壁異方性酸化プロセス

図 4 Ge フィン型チャネル形状 (矩形およびピーキング、高さ) と電流密度状態

# 表1. 過去の研究と本研究の電気特性の比較

|                       | 本研究              | 研究報告A            | 研究報告B            | 研究報告C         | 研究報告D            |

|-----------------------|------------------|------------------|------------------|---------------|------------------|

| 構造                    | ピーキングFinFET      | FinFET           | FinFET           | 全周ゲートFET      | 無接合全周ゲートFET      |

| フィン幅                  | 6 nm             | 13 nm            | 25 nm            | 3.5 nm        | 9 nm             |

| ゲート長                  | 40 nm            | 68 nm            | 60 nm            | 120 nm        | 280 nm           |

| S.S. (mV/dec)         | n-type: 70       | n-type: N.A.     | n-type: N.A.     | n-type: N.A.  | n-type: 150      |

|                       | p-type: 87       | p-type: 114      | p-type: 118      | p-type: 125   | p-type: 144      |

| PMOS $I_{ON}/I_{OFF}$ | >10 <sup>5</sup> | >10 <sup>5</sup> | >10 <sup>3</sup> | $>10^{3}$     | N.A.             |

| $(V_G; V_D)$          | (-2V; -0.1V)     | (-0.6V; -0.05V)  | (-1V; -0.05V)    | (-2V; -0.05V) |                  |

| NMOS $I_{ON}/I_{OFF}$ | >10 <sup>5</sup> | N.A.             | N.A.             | N.A.          | >10 <sup>5</sup> |

| $(V_G; V_D)$          | (2V; 0.1V)       |                  |                  |               | (2V; 0.05V)      |

#### 【用語解説】

#### (\*1) リーク電流

リーク電流とは、電子回路上で、絶縁されていて本来流れないはずの場所・経路で漏れ出す電流のことである。

#### (\*2) 中性粒子ビーム

通常のプラズマプロセスでは、高速な荷電粒子との反応を用いてプロセスが行われるので、衝突時に生じるダメージの他、電荷の蓄積や紫外光照射によるダメージ等が避けられないでいた。そのため電気的に中性な粒子を用いた酸化やエッチングなどがダメージを与えない究極のプロセス手法として注目されている。プラズマ中に存在する正イオンあるいは負イオンは電界により加速された場合には原子分子、電子、壁などとの衝突で電荷交換して中性化される。この時、運動エネルギーは保存され、方向性をもった中性粒子ビームが生成される。

# (\*3) サブスレッショルド・スイング (SS)

トランジスタにおいて、電流を一桁増加させるのに必要なゲート電圧の変化量を示す。この値が小さいほど、電流のオン・オフを急激に切り替えられる。従来の MOS トランジスタでは電子の熱拡散によりキャリアの注入を行うことから、サブスレッショルド・スイングは、60 mV/桁が物理的な下限である。

# (\*4) チャネル材料

半導体材料において電子や正孔が輸送される通り道のことをチャネルと呼ぶ。現在はシリコンが主流であるがより低電圧で高移動度を実現できるチャネル材料としてゲルマニウムやガリウムヒ素が検討されている。

# (\*5) 界面準位

ゲルマニウムとゲルマニウム酸化膜の境界では原子の結合手の数がうまく合わないので、どうしてもゲルマニウムや酸素の結合していない手ができてしまう。こういうところにゲルマニウム中の電子や正孔が捕らわれやすくなる。こういう異種の物質の界面にできて電子や正孔を捕まえるはたらきをするものを界面準位(または表面準位)と呼ぶ。

# (\*6) プロセスダメージ

半導体デバイス製造工程においてプラズマプロセスにより入るダメージが大きな問題となっている。ダメージには、(1)物理的なダメージ、(2)電荷蓄積によるダメージ、(3)放射光によるダメージ、の3種類がある。物理的ダメージは基板に入射するエネルギーをもったイオンの衝撃により基板に欠陥などのダメージが入ることをいう。電荷蓄積によるダメージはプラズマから基板に入射する電荷(正イオン、電子)が絶縁膜上に蓄積することで、MOSトランジスタにとって極めて重要であるゲート絶縁膜などを絶縁破壊することをいう。放射光によるダメージは、プラズマから基板に入射する紫外光やX線のような波長の短い放射光は基板に堆積されている絶縁膜中にホール・電子対を生成し、絶縁性を劣化させることをいう。

#### (\*7) プラズマプロセス

微細加工技術の一つで、プラズマにより励起された活性なイオンを、基板に垂直に入射するように加速して照射し、エッチングを行う。微細なパターンを垂直に加工できることから現在主流の加工方法であるが、イオンの照射や紫外線によるダメージが素子を劣化させる等が問題になりつつある。

# 【論文情報】

尚、今回の研究成果につきましては、12月5日から7日まで米国サンフランシスコで開催される国際電子デバイス会議 (IEDM: IEEE International Electron Device Meeting) において報告を行う予定です。

論文題目:High Performance Complementary Ge Peaking FinFETs by Room Temperature Neutral Beam Oxidation for Sub-7 nm Technology Node Applications

# 【問い合わせ先】

<研究に関すること>

東北大学原子分子材料高等研究機構 (WPI-AIMR)

東北大学流体科学研究所未到エネルギー研究センターグリーンナノテクノロジー研究分野 教授 寒川誠二

〒980-8577 仙台市青葉区片平2丁目1番1号

TEL/FAX: 022-217-5240

E-mail: samukawa@ifs.tohoku.ac.jp

# <報道担当>

東北大学原子分子材料科学高等研究機構(WPI-AIMR)

広報・アウトリーチオフィス

清水 修

Tel: 022-217-6146

E-mail: aimr-outreach@grp.tohoku.ac.jp